Год сдачи: 2009 Информация о файлах в архиве: ПЗ.doc - пояснительная записка к курсовому проекту

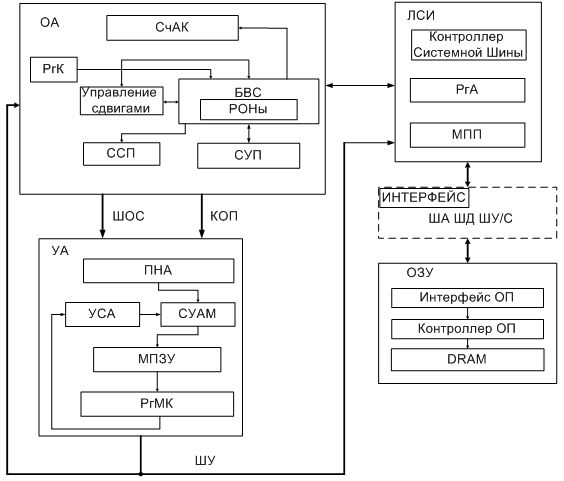

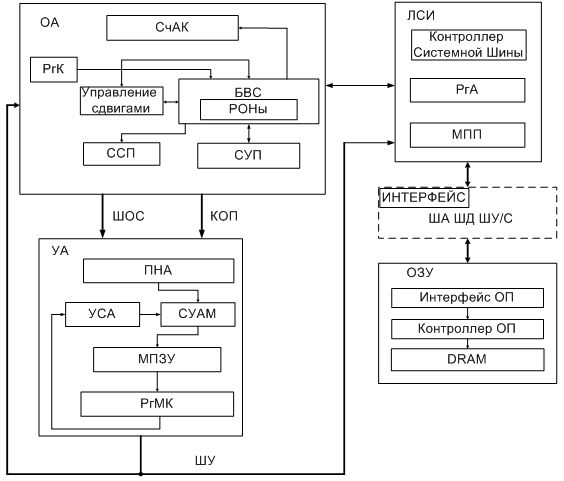

Структурная.vsd - схема электрическая структурная устройства

СтруктурнаяБОД.vsd - схема электрическая структурная блока обработки данных

Принципиальная.vsd - схема электрическая принципиальная оперативной памяти

Функциональная.vsd - схема электрическая функциональная оперативной памяти

Диаграмма.vsd - временные диаграммы регенерации оперативной памяти

БМУ.vsd - схема электрическая принципиальная блока микропрограммного управления

аннотация.doc - аннотация к курсовому проекту Краткое описание Цель курсового проекта состоит в приобретении практических навыков в проектировании блока обработки данных, управляющего автомата и интерфейса процессор-память процессора ЭВМ в соответствии с заданными в техническом задании архитектурными особенностями, а также в разработке технической документации, представленной пояснительной запиской и чертежами, выполненными в соответствии с ЕСКД.

Задание

Объектом курсового проектирования является блок обработки данных цифровой ЭВМ широкого назначения. Также необходимо продумать взаимодействие самого процессора и динамической памяти. Для этого следует выбрать подходящий интерфейс, исходя из объёма оперативной памяти. Важным элементом проектирования в данном случае является и шина данных ОП. По заданию она должна быть двунаправленной. Таким образом, можно выделить следующие этапы проектирования:

- разработка блока обработки данных нужной разрядности;

- синтез структуры операционных автоматов блоков обработки данных в базисе микропроцессорных секций (МПС);

- синтез управляющих автоматов с микропрограммируемой логикой,

- разработка организации и связей в ОП;

- управление ОП с помощью контроллера ОП;

- выбор подходящего интерфейса для взаимодействия процессор-память;

- разработка алгоритмов доступа к ОП ( регенерация, хранение);

- разработка электрических схем (структурной, функциональной и принципиальной) и оформление пояснительной записки.

Исходные данные для проектирования

Разработка БОД в структурном базисе серии 1804.

Длина слова операционного автомата 16 двоичных разрядов.

Микропрограммный автомат с объёмом МПЗУ не более 4,3 К слов.

Элементная база блока памяти –RAMD (FUJITSU MB8116E – 16К х 1).

Шина данных ОП двунаправленная, 16 двоичных разрядов.

Ёмкость ОП 64 Кб.

Разрядность регистра команд 24 бита.

Разрядность счётчика адреса команд 16 бит.

Интерфейс шины процессор-память – И-41.

Заключение

В ходе выполнения курсового проекта были приобретены навыки проектирования операционного и управляющего автоматов процессора ЭВМ. Результатом проектирования стал разработанный 16-разрядный секционированный микропроцессор, построенный в базисе МПС К1804ВС2. Также были приобретены навыки составления технической документации и выполнения чертежей по нормам ЕСКД.

На мой взгляд, одним из достоинств данного курсового проекта является то, что микропроцессор изучался и проектировался полностью, а не какой-либо его отдельный блок. Тем самым были определены и поняты связи и взаимодействие его компонентов, неотделимость их друг от друга. Особенно важными для этого оказалась организация взаимодействия ОП и БОДа через интерфейс.

Общая структура блока обработки данных

|